© A. Milenkovic

VHDL – VHSIC Hardware Description Language

```

Advanced VLSI Design

MUX Models (3)

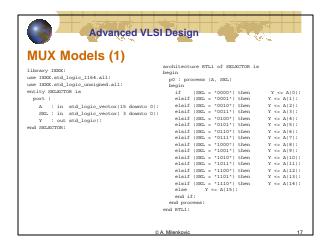

architecture RTL2 of SELECTOR is

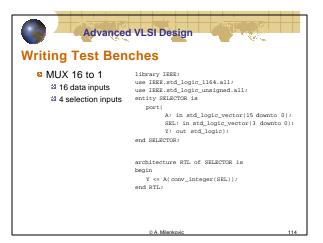

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.std_logic_unsigned.all;

entity SELECTOR is

when "0000" => Y <= A(0); when "0001" => Y <= A(1);

port (

: in std_logic_vector(15

when "0010" => Y <= A(2);

when "0011" => Y <= A(3);

SEL : in std_logic_vector( 3

downto 0);

when "0100" => Y <= A(4);

when "0101" => Y <= A(5);

when "0110" => Y <= A(6);

when "0111" => Y <= A(7);

: out std logic);

end SELECTOR;

when "1000" => Y <= A(8);

when "1001" => Y <= A(9);

when "1010" => Y <= A(10);

when "1011" => Y <= A(11);

when "1100" => Y <= A(12);

when "1101" => Y <= A(13);

when "1110" => Y <= A(14);

when others => Y <= A(15);

end case;

end process;

end RTL2;

```

```

Advanced VLSI Design

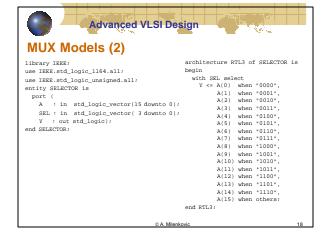

MUX Models (4)

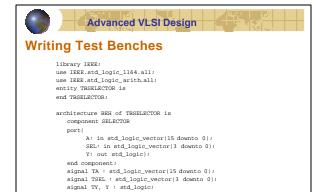

library IEEE:

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity SELECTOR is

port (

A : in std_logic_vector(15 downto 0);

SEL : in std_logic_vector(3 downto 0);

Y : out std_logic_vector(3 downto 0);

end SELECTOR;

```

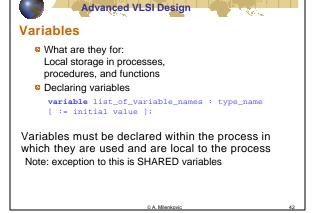

#### Signals

- Signals must be declared outside a process

- Declaration form

```

signal list_of_signal_names : type_name

[ := initial value ];

```

Declared in an architecture can be used anywhere within that architecture

A. Milenkovi

#### **Advanced VLSI Design**

#### Constants

Declaration form

```

constant constant_name : type_name := constant_value;

constant delay1 : time := 5 ns;

```

- Constants declared at the start of an architecture can be used anywhere within that architecture

- Constants declared within a process are local to that process

A. Milenkovic

#### **Advanced VLSI Design**

#### Variables vs. Signals

Variable assignment statements

expression is evaluated and the variable is instantaneously updated (no delay, not even delta delay)

variable\_name := expression;

· Signal assignment statement

```

signal_name <= expression [after delay];</pre>

```

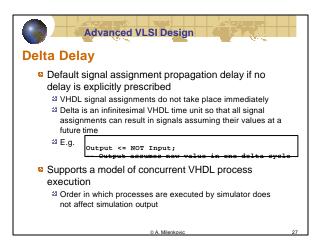

expression is evaluated and the signal is scheduled to change after delay; if no delay is specified the signal is scheduled to be updated after a delta delay

© A. Milenkovic

#### Advanced VLSI Design

#### Variables vs. Signals (cont'd)

# Process Using Variables

#### Variables entity dummy is

#### architecture vor of dummy is signal import, sum: integer:=0; begin process variable vor1; integer:=1; variable vor2; integer:=2; variable vor2; integer:=3;

begin wait on trigger; vor 1 = vor 2 + var 3; var 2 = var 1; var 3 = var 2; sun <= var 1 + var 2 + var 3;

end var: Sum = ?

end process:

#### **Process Using Signals**

entity durinty is

ent discrete sig of dummy is

signal trigger, sym: integer; =0;

signal trigger, sym: integer=0;

signal sig1: integer=2;

signal sig2: integer=2;

begin

placess

begin

sig1 = sig2 = sig

sum = ?

© A. Milenkovic

#### Advanced VLSI Design

#### **Predefined VHDL Types**

- Variables, signals, and constants can have any one of the predefined VHDL types or they can have a user-defined type

- Predefined Types

- bit −{'0', '1'}

- <sup>33</sup> integer − [-2<sup>31</sup> 1.. 2<sup>31</sup> − 1}

- <sup>24</sup> real −floating point number in range −1.0E38 to +1.0E38

- de character legal VHDL characters including loweruppercase letters, digits, special characters, ...

© A. Milenkovic

#### **Advanced VLSI Design**

# **User Defined Type**

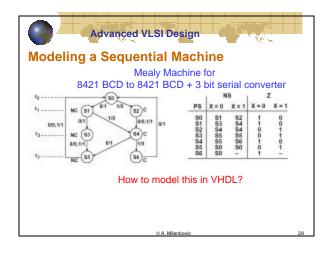

Common user-defined type is <u>enumerated</u>

```

type state_type is (S0, S1, S2, S3, S4, S5);

signal state : state_type := S1;

```

- If no initialization, the default initialization is the leftmost element in the enumeration list (S0 in this example)

- VHDL is strongly typed language => signals and variables of different types cannot be mixed in the same assignment statement, and no automatic type conversion is performed

© A. Milenkovic

4

#### **Arrays**

Example

```

type SHORT_WORD is array (15 downto 0) of bit;

signal DATA_WORD : SHORT_WORD;

variable ALT_WORD : SHORT_WORD := "010101010101010101";

constant ONE_WORD : SHORT_WORD := (others => '1');

```

- ALT\_WORD(0) rightmost bit

- ALT\_WORD(5 downto 0) low order 6 bits

- · General form

```

type arrayTypeName is array index_range of element_type;

signal arrayName : arrayTypeName [:=InitialValues];

```

© A. Milenkovic

#### **Advanced VLSI Design**

#### Arrays (cont'd)

Multidimensional arrays

```

type matrix4x3 is array (1 to 4, 1 to 3) of integer;

variable matrixA: matrix4x3 :=

((1,2,3), (4,5,6), (7,8,9), (10,11,12));

```

- matrixA(3, 2) = ?

- Unconstrained array type

```

type intvec is array (natural range<>) of integer;

type matrix is array (natural range<>),natural range<>)

```

• range must be specified when the array object is declared

```

signal intvec5 : intvec(1 to 5) := (3,2,6,8,1);

```

© A. Milenkovic

#### **Advanced VLSI Design**

#### **Predefined Unconstrained Array Types**

Bit\_vector, string

type bit\_vector is array (natural range <>) of bit; type string is array (positive range <>) of character;

constant string::string[i to 29] := "This string is 29 characters" |

constant A : bit\_vector(0 to 5) := "10101";

-- ('1', '0', '1', '0', '1');

- Subtypes

- include a subset of the values specified by the type

subtype SHORT\_WORD is : bit\_vector(15 to 0);

POSITIVE, NATURAL – predefined subtypes of type integer

A. Milenkovic

#### Advanced VLSI Design

#### **VHDL Operators**

- Binary logical operators: and or nand nor xor xnor

- Relational: = /= < <= > >=

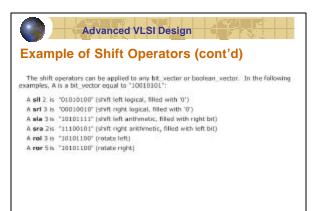

- Shift: sll srl sla sra rol ror

- Adding: + & (concatenation)

- Unary sign: + -

- Multiplying: \* / mod rem

- Miscellaneous: not abs \*\*

- Class 7 has the highest precedence (applied first), followed by class 6, then class 5, etc

A. Milenkovic

# Advanced VLSI Design

#### **Example of VHDL Operators**

In the following expression, A, B, C, and D are bit\_vectors: (A & not 8 or C ror 2 and D) = "110010"

The operators would be applied in the order:

not, 8, ror, or, and, =

If A = "110", B = "111", C = "011000", and D = "111011", the computation would proceed as follows:

not B = "000" (bit-by-bit complement)

A 8 not B = "110000" (concatenation)

C ror 2 = "000110" (rotate right 2 places)

(A & not 8) or (C ror 2) = "110110 (bit-by-bit or) (A & not 8 or C ror 2) and D = "110010" (bit-by-bit and)

[(A & not B or C ror 2 and D) = "L10010"] = TRUE (the parentheses force the equality test to be some last and the result is TRUE)

© A. Milenkovic

5

A. Milenkovic

© A. Milenkovic

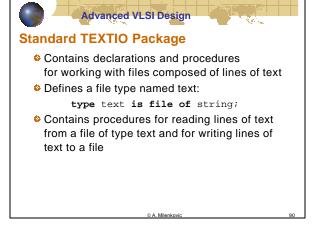

#### Reading TEXTIO file

- Readline reads a line of text and places it in a buffer with an associated pointer

- Pointer to the buffer must be of type line, which is declared in the textio package as:

- type line is access string;

- When a variable of type line is declared, it creates a pointer to a string

- Code

```

variable buff: line;

readline (test_data, buff);

a reads a line of text from test_data and places it in a buffer

which is pointed to by buff

```

© A. Milenkovio

#### **Advanced VLSI Design**

#### **Extracting Data from the Line Buffer**

- To extract data from the line buffer, call a read procedure one or more times

- For example, if bv4 is a bit\_vector of length four, the call

```

read(buff, bv4)

```

description extracts a 4-bit vector from the buffer, sets bv4 equal to this vector, and adjusts the pointer buff to point to the next character in the buffer. Another call to read will then extract the next data object from the line buffer.

#### **Advanced VLSI Design**

#### **Extracting Data from the Line Buffer** (cont'd)

- TEXTIO provides overloaded read procedures to read data of types bit, bit\_vector, boolean, character, integer, real, string, and time from buffer

- Read forms

- · read(pointer, value)

- read(pointer, value, good)

- agood is boolean that returns TRUE if the read is successful and FALSE if it is not

- at type and size of value determines which of the read procedures is called

- discharacter, strings, and bit\_vectors within files of type text ar e not delimited by quotes

A. Milenkovic

#### **Advanced VLSI Design**

### Writing to TEXTIO files

Call one or more write procedures to write data to a line buffer and then call writeline to write the line to a file

```

variable buffw : line;

variable int1 : integer;

variable bv8 : bit_vector(7 downto 0);

write(buffw, int1, right, 6); -- right just., 6 ch.

wide

write(buffw, bv8, right, 10);

writeln(buffw, output_file);

```

- Write parameters: 1) buffer pointer of type line,

- 2) a value of any acceptable type,

- 3) justification (left or right), and 4) field width (number of characters)

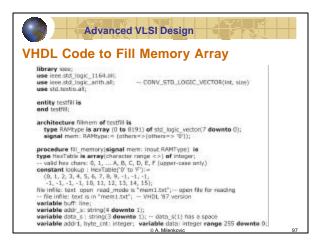

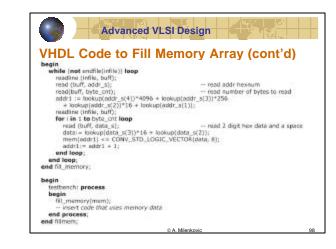

#### An Example

- Procedure to read data from a file and store the data in a memory array

- Format of the data in the file

- address N comments

byte1 byte2 ... byteN comments

- address 4 hex digits

- N indicates the number of bytes of code

- bytei 2 hex digits

- · each byte is separated by one space

- · the last byte must be followed by a space

- · anything following the last state will not be read and will be treated as a comment

#### **Advanced VLSI Design**

#### An Example (cont'd)

- Code sequence: an example

- 4 12AC 7 (7 hex bytes follow)

AE 03 B6 91 C7 00 OC (LDX imm, LDA dir, STA ext) 005B 2 (2 bytes follow)

- TEXTIO does not include read procedure for hex numbers

- a we will read each hex value as a string of characters and then convert the string to an integer

- How to implement conversion?

- table lookup constant named lookup is an array of integers indexed by characters in the range '0' to 'F'

- this range includes the 23 ASCII characters: '0', '1', ... '9', ':', ';', '<', '=', '>', '?', '@', 'A', ... 'F'

- · corresponding values: 0, 1, ... 9, -1, -1, -1, -1, -1, -1, 10, 11, 12, 13, 14, 15

© A. Milenkovio

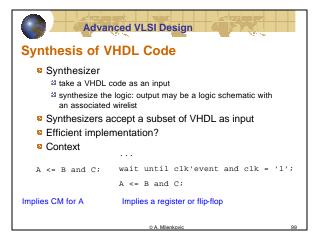

#### Assert Statement

Checks to see if a certain condition is true, and if not causes an error message to be displayed

```

assert boolean-expression

report string-expression

severity severity-level;

```

- Four possible severity levels

- ₩ NOTE

- **≅** WARNING

- # ERROR

- ≝ FAILURE

- Action taken for a severity level depends on the simulator

© A. Milenkovic

A Milankovic 11

#### **Advanced VLSI Design**

#### **Writing Test Benches**

```

begin

p0: process

variable cnt : std_logic_vector(4 downto 0);

begin

for j in 0 to 31 loop

cnt := conv_std_logic_vector(j, 5);

TSEL <= cnt(3 downto 0);

Y <= cnt(4);

A <= (A'range => not cnt(4));

A(conv_integer(cnt(3 downto 0))) <= cnt(4);

wait for PERIOD;

end loop;

wait;

end process;</pre>

```

© A. Milenkovic 1

#### Advanced VLSI Design

constant PERIOD : time := 50 ns; constant STROBE : time := 45 ns;

### Writing Test Benches

```

begin

check: process

variable err_cnt : integer := 0;

begin

wait for STROBE;

for j in 0 to 31 loop

assert FALSE report "comparing" severity NOTE;

if (Y /= TY) then

assert FALSE report "not compared" severity WARNING;

err_cnt := err_cnt + 1;

end if;

wait for PERIOD;

end loop;

assert (err_cnt = 0) report "test failed" severity ERROR;

assert (err_cnt /= 0) report "test passed" severity NOTE;

wait;

end process;

sell: SELECTOR port map (A => TA, SEL = TSEL, Y => TY);

end BER;

```

A. Milenkovic

#### Advanced VLSI Design

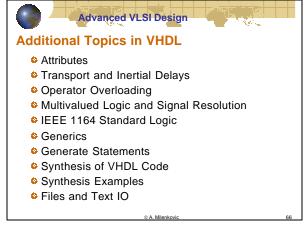

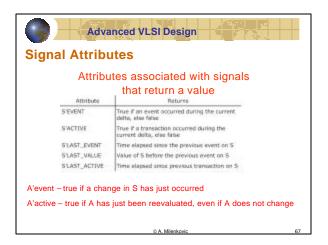

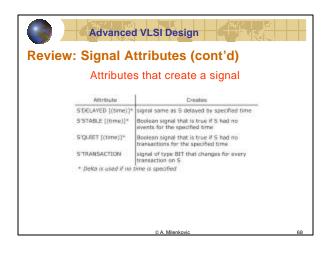

# Attributes associated to signals

- allow checking for setup, hold times,

- and other timing specifications

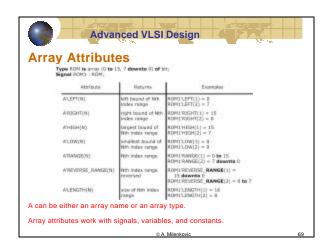

- Attributes associated to arrays

- allow us to write procedures that do not depend on the manner in which arrays are indexed

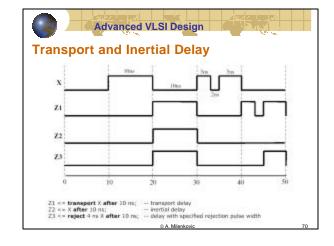

- Inertial and transport delays

- allow modeling of different delay types that occur in real systems

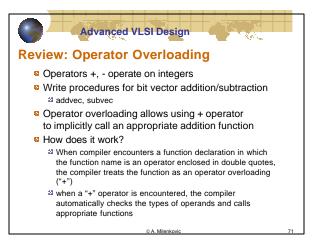

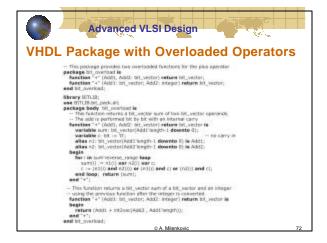

- Operator overloading

- allow us to extend the definition of VHDL operators so that they can be used with different types of operands

A. Milenkovic

#### **Advanced VLSI Design**

#### Things to Remember (cont'd)

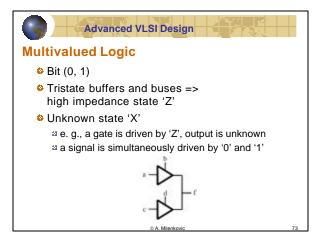

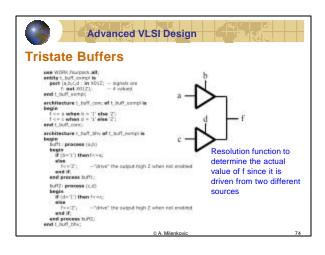

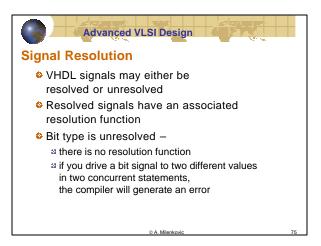

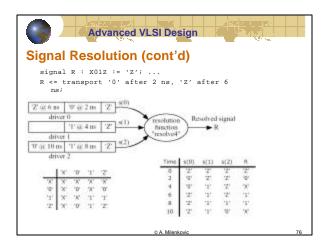

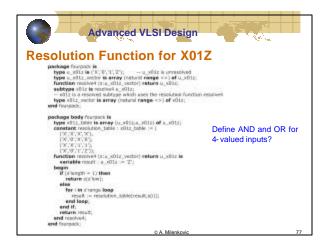

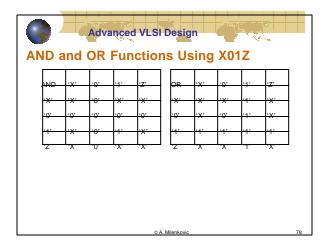

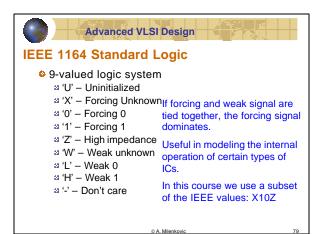

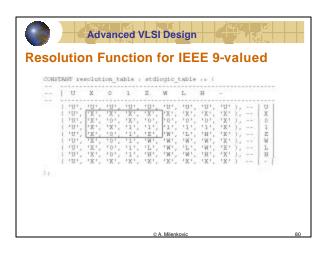

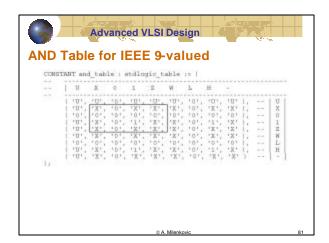

- Multivalued logic and the associated resolution functions

- allow us to model tri-state buses, and systems where a signal is driven by more than one source

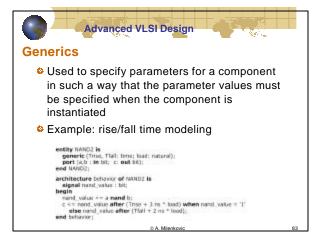

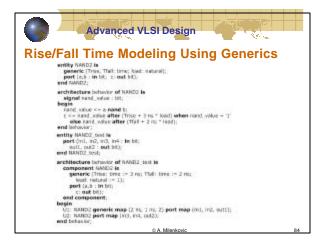

- Generics

- allow us to specify parameter values for a component when the component is instantiated

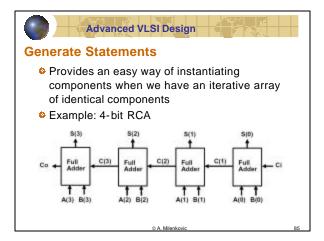

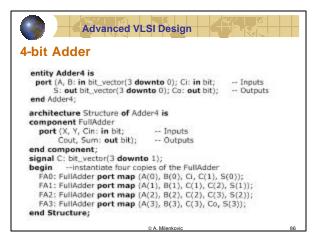

- Generate statements

- all efficient way to describe systems with iterative structure

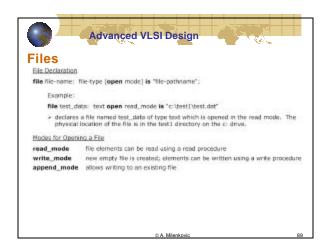

- TEXTIO

- a convenient way for file input/output

A. Milenkovic